Evolving the DSA of semiconductor RSD

Leveraging data and analytics to create next generation R&D

kpmg.com/semiconductors

### About the authors

**Scott Jones** is a Principal in KPMG in the U.S.'s Technology, Media & Telecommunications Strategy practice. He has over 15 years of experience, including program management in the semiconductor industry, as an equity analyst covering the semiconductor sector, and

serving technology companies as a consultant. Scott has delivered performance improvement services for his clients in areas such as R&D portfolio management, financial modeling of advanced technologies, M&A strategy, post-merger integration, and operating model transformation.

**Arun Ghosh** is a Principal in KPMG in the U.S. focused on driving business value leveraging analytics, automation, AI, and blockchain. Arun's work and experience covers the high-tech and life sciences industries, including defining, designing, and delivering transformation

programs across commercial, core operations, R&D, manufacturing, and supply chain business functions. He is also a frequent speaker at industry forums. Semiconductor CFOs, strategy, and corporate development professionals should incorporate D&A and Agile methodology into the R&D process. This can yield better ROI, bring more profitable products to market faster, and become a competitive advantage. With semiconductor R&D costs rising, there is no time to waste in evolving the R&D process.

# Evolving the D&A of semiconductor R&D

### **R&D costs spiraling**

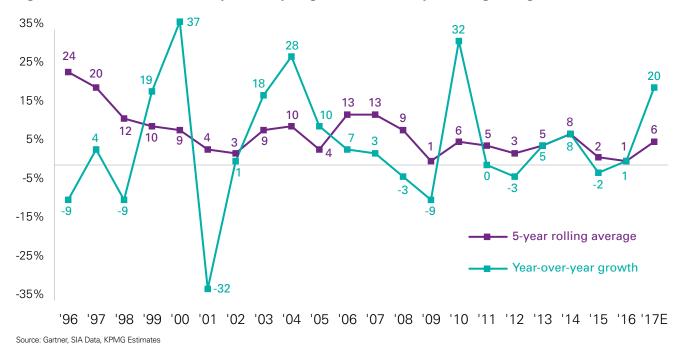

It is well known that semiconductor companies reinvest a tremendous percentage of revenue back into research and development (R&D) to sustain the breakneck pace of innovation that has driven the industry for the past 50 years. In 2015 and 2016, U.S. semiconductor companies invested over 18 percent of revenue in R&D<sup>1</sup>. 2017 will be a banner year for the semiconductor industry with revenues expected to grow by almost 20 percent<sup>2</sup> to over US\$400 billion, the highest growth since 2010. So if past trends hold true, R&D investment will also be at a historic level. The 2017 revenue growth has been triggered by favorable memory pricing and the first PC refresh cycle since tablets have come to the market. But historically, the semiconductor industry grew by an average of 5 percent annually from 2008 to 2017, down from the 11 percent average growth in the 90s leading up to the financial crisis. After higher than expected growth in 2017, growth in subsequent years is expected to normalize to 4–5 percent. As we look ahead into the future, the trends highlighted below and their implications will shape the landscape of the semiconductor industry.

1 Semiconductor Industry Association (SIA) 2016 and 2017 Factbooks

<sup>2</sup> Gartner, "Semiconductor Forecast Database, Worldwide, 3Q17 Update" (October 2017)

Despite revenue growth fluctuations, R&D costs continue to rise, particularly on the leading edge. Increasing difficulty in achieving the improvements promised by Moore's law and insatiable consumer demand for more features and functionalities have led to R&D costs outpacing revenue growth. So far the main response has been incremental improvements to the traditional approach to R&D and more recently, a wave of consolidation through mergers and acquisitions (M&A) that has allowed companies to scale their R&D across broader revenue streams.

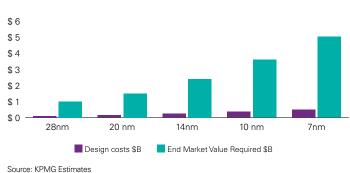

Figure 2 highlights how product development costs have risen as development has transitioned from one node to the next. On average, product development on 7nm is expected to cost ~30 percent more than that on 10nm. Rising costs in the development cycles raise the stakes as companies must meet time-to-market goals to capture the necessary market share to justify spending from a return on investment (ROI) perspective as growth in traditional segments plateaus.

### Figure 2: End markets required to support design costs (Value in Billions)

Note: Assuming 65nm as baseline

As an example, a \$400 million investment in a new product development requires a company to address a market of \$5 billion and capture ~\$1 billion in market share to break even (assuming 20 percent market share with 40 percent margins). There are very few market segments that can support this level of investment, that is forcing companies to explore diversification. But diversification leads to new generations of chips that are harder to make because they have to address multiple market segments, adding to the complexity and expense.

### **R&D** budgets challenged by new products

For the past decade, smartphones and then tablets drove growth in the wireless segment, allowing wireless to overtake PCs as the largest end market for semiconductors. When PC and smartphone demand was high, refresh cycles followed very predictable patterns. A one-year cadence for new designs was common, and those went into a relatively small number of product configurations by a small group of prominent semiconductor buyers. PCs and smartphones are still the largest markets, but revenue growth has stagnated due to market penetration, longer refresh cycles, and lower consumer pricing.

Recently, the end markets driving semiconductor growth have shifted. Today's growth is being fueled by diverse markets such as automotive, industrial, and the spectrum of Internet of Things (IoT) devices. And all are incorporating connectivity, artificial intelligence (AI), and increased sensor content. These products have a wide range of use cases and configurations, creating the demand for an even greater variety of semiconductor products and capabilities.

Semiconductor companies are realigning their business models and R&D efforts to match this new landscape. In order to be successful, semiconductor companies must be more nimble in developing an optimized number of platforms and products that serve these new, broader end markets. The same design architecture that services the smartphone market needs to be easily leveraged to support drones, wearables, and early efforts in the autonomous car market. Proper R&D discipline is imperative. Chasing multiple new product opportunities without a clear ROI projection can delay the truly key programs and balloon into multiple generations of delayed products. This can lead to market share loss or aggressive price discounting. In either case, fewer margin dollars jeopardizes future R&D investment, creating a downward spiral that snowballs with each misjudged product cycle.

### How to improve R&D efficiency with Agile and D&A

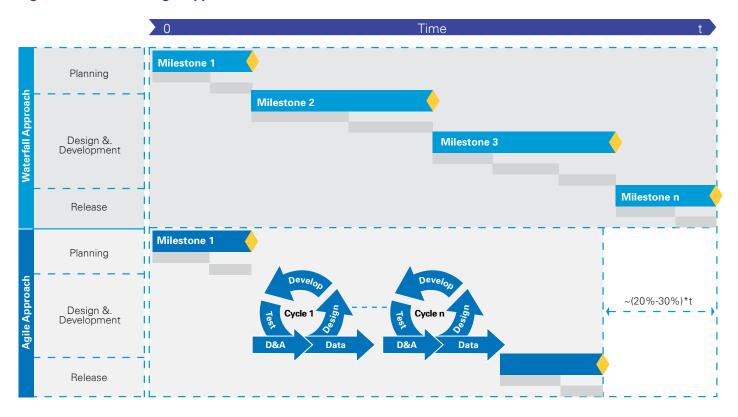

We have found that applying Agile methodologies can yield tremendous value to the semiconductor R&D planning and product development process. Agile is a timed, iterative approach (typically used in software development) that builds products/functionality incrementally from the start, rather than trying to deliver a final, finished product all at once at the end. Any Agile process requires strong up-front requirements and close coordination between the teams working on the various product modules. This ensures that the modules come together harmoniously for all the different products and customers.

If semiconductor companies are thinking of their R&D process like the milestones in a waterfall development approach, the risk of these modules not integrating becomes too high. An Agile-based approach featuring continuous integration is ideal. Increased cycles of communication and refinement will dramatically lower the risk of creating an off-base end product.

This sounds pretty straightforward, but there are significant challenges. These product modules are typically developed by different teams located in design centers all over the world. The tools and intellectual property (IP) best suited for one module may not be the same for another module. This results in a variety of design platforms with varying data formats residing in many places. These are barriers to realizing the benefits that can be achieved through more frequent Agile cycles of learnings.

Current data and analytics (D&A) applications have the ability to not only manage and consolidate data sets on the scale of a design database, but also unlock insights and highlight risks that would not have been seen until much later in the development life cycle. These insights are unlocked through leveraging D&A in areas such as regression testing, where it can improve regression coverage and increase the learnings from each iteration, reducing the number of iterations required to validate various portions of the design database. Our research indicates that such automation helps companies shorten the design life cycle by at least one to three months and also eliminates certain elements of overhead development and guality assurance (QA) costs. Applying D&A to gain advantages in continuous Agile integration is one the primary ways that chip design companies can combat the increased complexity and cost of leading edge system-on-achip (SoC) designs.

### Figure 3: Waterfall vs. Agile approaches

### **Case study**

KPMG in the U.S. delivered an analytics platform for a leading SoC design company. The platform centralizes

disparate test data across functional design teams onto a single advanced analytics platform. Using this platform:

- Designers can analyze design databases to account for the inherent varieties in the data across cores and chips at multiple stages of the design life cycle

- Product managers can visualize core and chip status at a glance, eliminating subjective reporting processes. This provides greater visibility into dependencies between teams, avoiding last-minute scrambles and the risk of controls not being applied due to manual processes.

- Executives can gain greater insight into risks and delays, enabling proactive decision making to manage resources and customer commitments

### Integrating D&A into R&D

Use of D&A in semiconductor R&D is not just limited to the cycles of continuous integration. Leveraging effective D&A helps unlock insights into improving R&D processes. For example, real-time insights into project bottlenecks allows companies to adjust staffing levels, analyze productivity drag, and make organizational and operational changes within R&D to improve net productivity. Thus, D&A can play an important role in streamlining and optimizing R&D processes and is a significant lever for managing R&D spend and improving business performance.

The sheer volume of data collected during product development is staggering. Many organizations recognize the potential value of the data but have little idea how they can manage the massive volume of it. The physical design stage alone can generate close to 2PB of raw test results. In another example, testing for 50 different parameters on a wafer with 10,000 chips generates 500K data points per wafer. With 25 wafers in one lot, it can grow to 12.5 million data points. If you imagine testing 10 lots per day leading to 125 million data points, you can quickly realize the size of the problem that exists in analyzing this data.

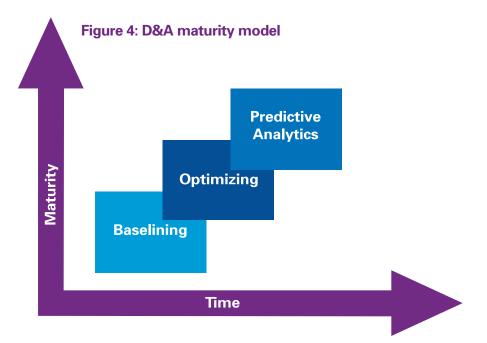

Even companies that have effective data management practices use only a very small percentage of the data available. This requires change in how decision makers perceive D&A. It starts with asking the right strategic questions before seeking and analyzing the most pertinent data. A structured approach can help R&D organizations make better decisions by using accurate and reliable information to assess opportunities and risks, optimize existing processes, and predict potential failures.

### By integrating Agile development and D&A into their R&D processes, semiconductor companies can position themselves for a competitive advantage through:

- Time to market shortened design, continuous integration, and validation cycles enabled by Agile and D&A

- Improved ROI on R&D spend more efficient use of R&D resources and prioritization of the most important programs

- Increased productivity D&A empowering faster cycles of learning generated from the design databases across various teams and locations

- Lower execution risk use of common platforms ensure better integration of the design databases and lower risk of errors or delays when integrating design blocks from various components

## Actions to take

Start by understanding all the product development methodologies being used along with the source and use of various data that's being generated. You ultimately want to achieve the right balance between Agile and traditional product development methodologies, but first you need to fully understand your current state.

Determine the essential data points. Prior to interpretation, analytics platforms must define which data points are most critical at each milestone in each product development process and at which level (core vs. chip). This complex logic will later need to be synthesized to give an overall view of the status, quality, and development cost (depending on the data available) of an entire chip.

Establish an agnostic and adaptable platform to gather essential data. D&A requires an ecosystem that funnels data into a central point and finds common anchors to measure it. Leading semiconductor companies are establishing format-agnostic, flexible, scalable platforms to gather data from multiple sources such as design verification, system validation, wafer test, and product test. This infrastructure is necessary to progress the business as it learns more about its own data and processes. **Establish a baseline.** After achieving a heightened state of awareness through systems able to make sense of their data, companies should establish their baseline of current-state performance. Data gathered from baselining can then be used for future continuous improvements and process optimization. In the most mature phase, companies can utilize D&A to become contextually aware of the competitive landscape and market forces and implement predictive analytics.

Once all the foundational elements are in place and analytics are being used efficiently, semiconductor companies can begin to realize the full potential of design optimization and drive the R&D efficiencies discussed earlier. Insights generated from the consolidated databases will allow R&D organizations to continue to innovate and meet the demands of the everchanging market.

### How KPMG can help

### **Global Semiconductor practice**

Our network of professionals has extensive experience working with global semiconductor and technology companies ranging from the FORTUNE 500 to pre-IPO (initial public offering) start-ups. In addition to providing audit, tax, and advisory services, KPMG firms aim to go beyond today's challenges to anticipate the potential long- and short-term consequences of shifting business, technology, and financial strategies. KPMG continues to build on our member firms' successes thanks to our clear vision, values, and more than 189,000 people in 152 countries. We have the knowledge and experience to navigate the global landscape.

KPMG's Strategy practice focuses on delivering corporate and private equity strategies based on our proprietary 9 Levers of Value framework, along with implementation that helps companies get from strategy to results. KPMG firms' dedicated strategy professionals have deep strategic advisory experience, particularly in building equity value and accelerating growth.

### **Global D&A**

In a global environment defined by constant disruption, business leaders need D&A they can trust to inform their most important decisions. KPMG's D&A team has earned that trust with an evidence-based, business-first approach that is at our core. For more than 100 years, we have worked across industries to help member firms' clients address their long-term, strategic objectives. And as an internationally regulated accounting and professional services network, our member firms have an unwavering commitment to precision and quality in everything we do.

### **Contact us:**

### Tim Zanni

Global and U.S. Technology Sector Leader Chair of Global and U.S. TMT Line of Business KPMG in the U.S. 408-367-4100 tjzanni@kpmg.com

### **Lincoln Clark**

Partner in charge Global semiconductor practice KPMG in the U.S. 408-367-4914 lincolnclark@kpmg.com

### Scott Jones

Principal, Advisory Global semiconductor practice KPMG in the U.S. 408-367-7002 asjones@kpmg.com

#### Arun Ghosh

Principal, Advisory KPMG in the U.S. 617-988-1628 arunghosh@kpmg.com

Some or all of the services described herein may not be permissible for KPMG audit clients and their affiliates.

The information contained herein is of a general nature and is not intended to address the circumstances of any particular individual or entity. Although we endeavor to provide accurate and timely information, there can be no guarantee that such information is accurate as of the date it is received or that it will continue to be accurate in the future. No one should act upon such information without appropriate professional advice after a thorough examination of the particular situation. The KPMG name and logo are registered trademarks or trademarks of KPMG International.

© 2017 KPMG International Cooperative ("KPMG International"), a Swiss entity. Member firms of the KPMG network of independent firms are affiliated with KPMG International. KPMG International provides no client services. No member firm has any authority to obligate or bind KPMG International or any other member firm vis-à-vis third parties, nor does KPMG International have any such authority to obligate or bind any member firm. All rights reserved. Printed in the U.S.A. NDPPS 725495